- 您現在的位置:買賣IC網 > PDF目錄373918 > AD7825BN (ANALOG DEVICES INC) 3 V/5 V, 2 MSPS, 8-Bit, 1-, 4-, 8-Channel Sampling ADCs PDF資料下載

參數資料

| 型號: | AD7825BN |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | ADC |

| 英文描述: | 3 V/5 V, 2 MSPS, 8-Bit, 1-, 4-, 8-Channel Sampling ADCs |

| 中文描述: | 4-CH 8-BIT FLASH METHOD ADC, PARALLEL ACCESS, PDIP24 |

| 封裝: | 0.300 INCH, PLASTIC, MS-001AF, DIP-24 |

| 文件頁數: | 12/18頁 |

| 文件大小: | 215K |

| 代理商: | AD7825BN |

AD7822/AD7825/AD7829

–12–

REV. A

OPERATING MODES

The AD7822, AD7825, and AD7829 have two possible modes

of operation, depending on the state of the

CONVST

pulse

approximately 100 ns after the end of a conversion, i.e., upon

the rising edge of the

EOC

pulse.

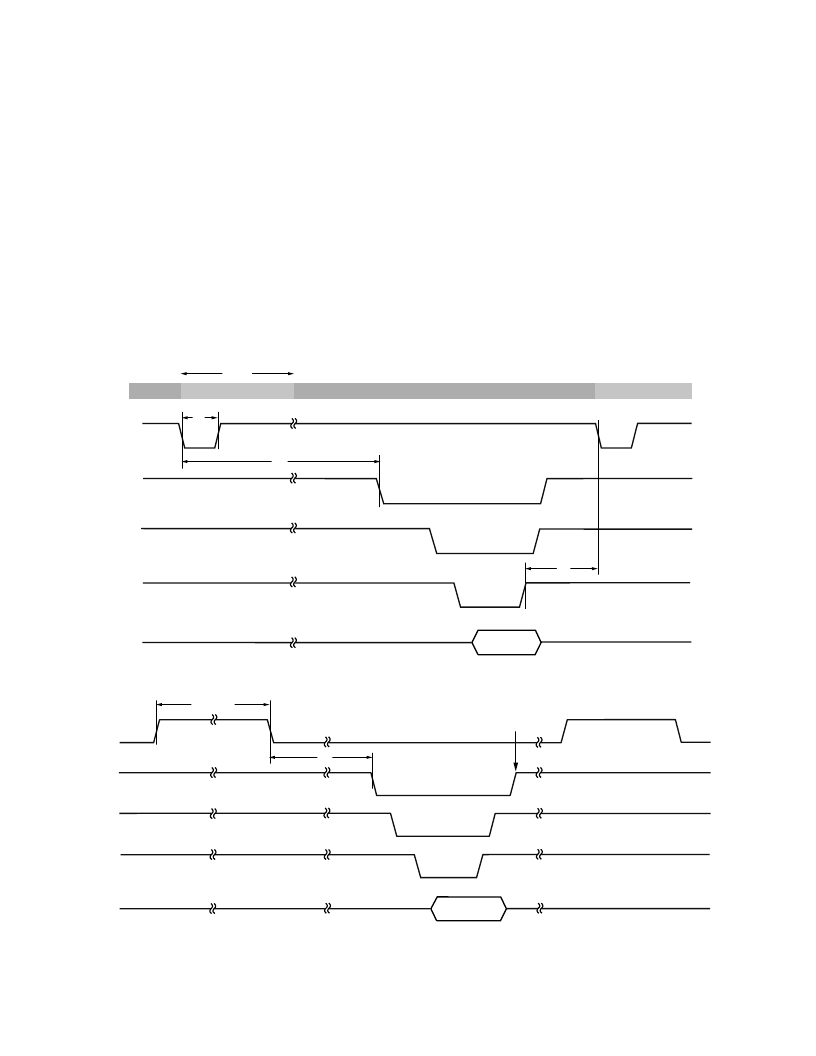

Mode 1 Operation (High Speed Sampling)

When the AD7822, AD7825, and AD7829 are operated in

Mode 1 they are not powered-down between conversions. This

mode of operation allows high throughput rates to be achieved.

Figure 20 shows how this optimum throughput rate is achieved

by bringing

CONVST

high before the end of a conversion, i.e.,

before the

EOC

pulses low. When operating in this mode a new

conversion should not be initiated until 30 ns after the end of a

read operation. This is to allow the track/hold to acquire the

analog signal to 0.5 LSB accuracy.

Mode 2 Operation (Automatic Power-Down)

When the AD7822, AD7825, and AD7829 are operated in

Mode 2 (see Figure 21), they automatically power down at the

end of a conversion. The

CONVST

signal is brought low to ini-

tiate a conversion and is left logic low until after the

EOC

goes

high, i.e., approximately 100 ns after the end of the conversion.

The state of the

CONVST

signal is sampled at this point (i.e.,

530 ns maximum after

CONVST

falling edge) and the AD7822,

AD7825, and AD7829 will power down as long as

CONVST

is low. The ADC is powered up again on the rising edge of the

CONVST

signal. Superior power performance can be achieved

in this mode of operation by only powering up the AD7822,

AD7825, and AD7829 to carry out a conversion. The parallel

interface of the AD7822, AD7825, and AD7829 is still fully

operational while the ADCs are powered down. A read may occur

while the part is powered down, and so it does not necessarily

need to be placed within the

EOC

pulse as shown in Figure 21.

t

2

t

1

t

3

VALID

DATA

CONVST

EOC

CS

RD

DB0-DB7

TRACK

HOLD

TRACK

HOLD

120ns

Figure 20. Mode 1 Operation

CONVST

EOC

CS

RD

DB0-DB7

t

POWER-UP

t

1

VALID

DATA

POWER

DOWN

HERE

Figure 21. Mode 2 Operation

相關PDF資料 |

PDF描述 |

|---|---|

| AD7825BR | 3 V/5 V, 2 MSPS, 8-Bit, 1-, 4-, 8-Channel Sampling ADCs |

| AD7825BRU | 14-Bit 48KSPS DAS with ADC, MUX, PGA and Internal Reference 28-SSOP -40 to 85 |

| AD7822BN | 3 V/5 V, 2 MSPS, 8-Bit, 1-, 4-, 8-Channel Sampling ADCs |

| AD7822BR | 3 V/5 V, 2 MSPS, 8-Bit, 1-, 4-, 8-Channel Sampling ADCs |

| AD7822BRU | 3 V/5 V, 2 MSPS, 8-Bit, 1-, 4-, 8-Channel Sampling ADCs |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD7825BNZ | 制造商:Analog Devices 功能描述:ADC Single Semiflash 2Msps 8-bit Parallel 24-Pin PDIP 制造商:Analog Devices 功能描述:IC 8BIT ADC 7825 DIP24 |

| AD7825BNZ | 制造商:Analog Devices 功能描述:IC |

| AD7825BNZ1 | 制造商:AD 制造商全稱:Analog Devices 功能描述:3 V/5 V, 2 MSPS, 8-Bit, 1-/4-/8-Channel Sampling ADCs |

| AD7825BR | 制造商:Analog Devices 功能描述:ADC Single Semiflash 2Msps 8-bit Parallel 24-Pin SOIC W 制造商:Analog Devices 功能描述:IC 8-BIT ADC |

| AD7825BR-REEL | 制造商:Analog Devices 功能描述:ADC Single Semiflash 2Msps 8-bit Parallel 24-Pin SOIC W T/R |

發布緊急采購,3分鐘左右您將得到回復。