- 您現在的位置:買賣IC網 > PDF目錄373939 > AD8178 (Analog Devices, Inc.) 450 MHz, Triple 16 】 5 Video Crosspoint Switch PDF資料下載

參數資料

| 型號: | AD8178 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | 450 MHz, Triple 16 】 5 Video Crosspoint Switch |

| 中文描述: | 450兆赫,三16】5視頻交叉點開關 |

| 文件頁數: | 19/40頁 |

| 文件大小: | 545K |

| 代理商: | AD8178 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

AD8178

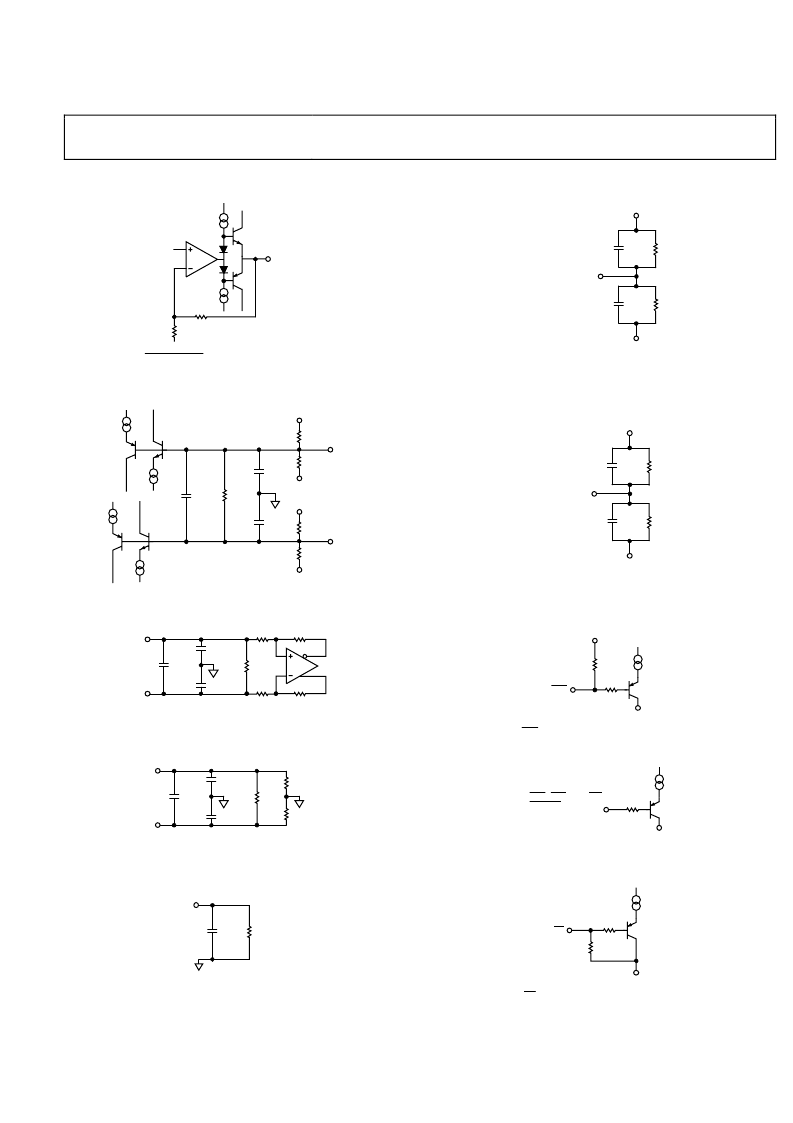

EQUIVALENT CIRCUITS

Rev. 0 | Page 19 of 40

0

1k

(VPOS – VNEG)

2

1k

OPn, ONn

Figure 8. Enabled Output (see also ESD Protection Map, Figure 19)

0

0.4pF

3.1k

20k

20k

3.4pF

3.4pF

OPn

VPOS

VNEG

20k

20k

VPOS

VNEG

ONn

Figure 9. Disabled Output (see also ESD Protection Map, Figure 19

)

0

1.3pF

1.3pF

0.3pF

IPn

INn

10k

2500

2500

5050

5050

Figure 10. Receiver Differential (see also ESD Protection Map, Figure 19)

0

1.3pF

1.3pF

0.3pF

IPn

INn

10k

2500

2500

Figure 11. Receiver Simplified Equivalent Circuit When Driving Differentially

0

1.6pF

IPn

INn

2.5k

Figure 12. Receiver Simplified Equivalent Circuit When Driving Single-Ended

0

0.1pF

VPOS

10k

0.1pF

10k

VNEG

VBLK,

VOCM_CMENCOFF

Figure 13. VBLK and VOCM_CMENCOFF Inputs

(see also ESD Protection Map, Figure 19)

0

0.3pF

VPOS

3.33k

0.3pF

3.33k

VNEG

VOCM_CMENCON

Figure 14. VOCM_CMENCON Input (see also ESD Protection Map, Figure 19

)

0

RST

VDD

DGND

1k

25k

Figure 15. RST Input (see also ESD Protection Map, Figure 19)

0

CLK, SER/PAR, WE,

UPDATE, SERIN

A[2:0], D[4:0],

CMENC

DGND

1k

Figure 16. Logic Input (see also ESD Protection Map, Figure 19)

DGND

1k

25k

CS

0

Figure 17. CS Input (see also ESD Protection Map, Figure 19)

發布緊急采購,3分鐘左右您將得到回復。