- 您現在的位置:買賣IC網 > PDF目錄373967 > AD9786BSVRL (ANALOG DEVICES INC) 16-Bit, 200 MSPS/500 MSPS TxDAC+ with 2】/4】/8】 Interpolation and Signal Processing PDF資料下載

參數資料

| 型號: | AD9786BSVRL |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | DAC |

| 英文描述: | 16-Bit, 200 MSPS/500 MSPS TxDAC+ with 2】/4】/8】 Interpolation and Signal Processing |

| 中文描述: | PARALLEL, WORD INPUT LOADING, 16-BIT DAC, PQFP80 |

| 封裝: | PLASTIC, MS-026-ADD, TQFP-80 |

| 文件頁數: | 27/60頁 |

| 文件大小: | 1497K |

| 代理商: | AD9786BSVRL |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁當前第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁

AD9786

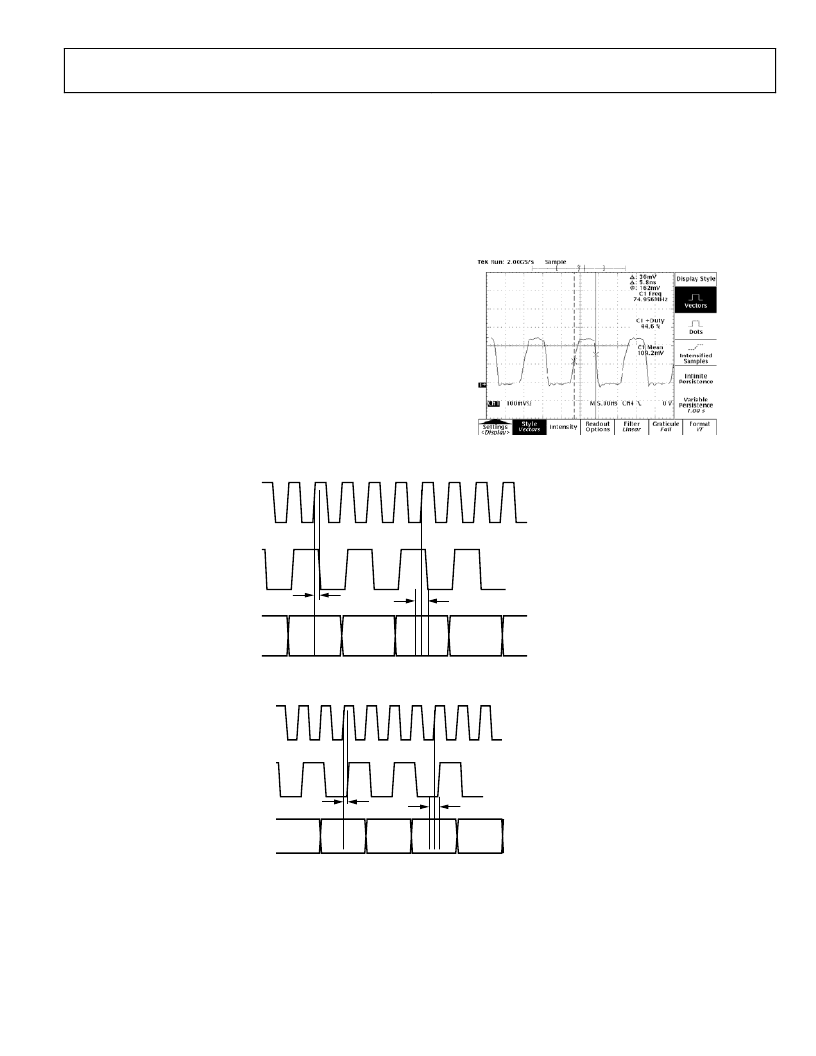

With the interpolation set to 2×, the DACCLK input runs at

twice the speed of the DATACLK. Data is latched into the

digital inputs of the AD9786 on every other rising edge of

DACCLK, as shown in Figure 47 and Figure 48. With

DCLKPOL = 0, as shown in Figure 47, the latching edge of

DACCLK is the rising edge that occurs just before the falling

edge of DATACLK. With DCLKPOL = 1, as in Figure 48, the

latching edge of DACCLK is the rising edge of DACCLK that

occurs just before the rising edge of DATACLK. The setup

and hold time values are identical to those in Figure 44 and

Figure 45.

Rev. 0 | Page 27 of 60

Note that there is a slight difference in the delay from the rising

edge of DACCLK to the falling edge of DATACLK, and the

delay from the rising edge of DACCLK to the rising edge of

DATACLK. As Figure 46 shows, the DATACLK duty cycle is

slightly less than 50%. This is true in all modes.

With the interpolation set to 4× or 8×, the DACCLK input runs

at 4× or 8× the speed of the DATACLK output. The data is

latched in on a rising edge of DACCLK, similar to the 2×

interpolation mode. However, the latching edge is every fourth

edge in 4× interpolation mode and every eighth edge in the 8×

interpolation mode. Similar to operation in the 2× interpolation

mode, with DCLKPOL = 0, the latching edge of DACCLK is the

rising edge that occurs just before the falling edge of

DATACLK. With DCLKPOL = 1, the latching edge of DACCLK

is the rising edge that occurs just before the rising edge of

DATACLK. The setup and hold time values are identical to

those in 1× and 2× interpolation.

0

Figure 46.

t

D

= 5ns TYP

t

S

= –0.5ns MIN

t

H

= 2.9ns MIN

DACCLK

IN

DATACLK

OUT

DATA

0

Figure 47. Data Timing, 2× Interpolation, DCLKPOL = 0

0

t

D

= 6ns TYP

t

H

= 2.9ns MIN

t

S

= –0.5ns MIN

DACCLK

IN

DATACLK

OUT

DATA

Figure 48. Data Timing, 2× Interpolation, DCLKPOL = 1

相關PDF資料 |

PDF描述 |

|---|---|

| AD9801 | CCD Signal Processor For Electronic Cameras(用于電子照相機的CCD信號處理器) |

| AD9802JST | Silver Mica Capacitor; Capacitance:10pF; Capacitance Tolerance: 5%; Series:CD17; Voltage Rating:500VDC; Capacitor Dielectric Material:Mica; Termination:Radial Leaded; Lead Pitch:5.9mm; Leaded Process Compatible:Yes RoHS Compliant: Yes |

| AD9802 | .50" x 50 Black/Clear 240 Industrial Label Supply RoHS Compliant: NA |

| AD9803 | CCD And Video Signal Processor For Electronic Cameras(電子照相機的CCD信號和視頻信號處理器) |

| AD9805 | Complete 12-Bit/10-Bit 6 MSPS CCD/CIS Signal Processors |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD9786BSVZ | 功能描述:IC DAC 16BIT INTERPOL/SP 80TQFP RoHS:是 類別:集成電路 (IC) >> 數據采集 - 數模轉換器 系列:TxDAC+® 標準包裝:1 系列:- 設置時間:4.5µs 位數:12 數據接口:串行,SPI? 轉換器數目:1 電壓電源:單電源 功率耗散(最大):- 工作溫度:-40°C ~ 125°C 安裝類型:表面貼裝 封裝/外殼:8-SOIC(0.154",3.90mm 寬) 供應商設備封裝:8-SOICN 包裝:剪切帶 (CT) 輸出數目和類型:1 電壓,單極;1 電壓,雙極 采樣率(每秒):* 其它名稱:MCP4921T-E/SNCTMCP4921T-E/SNRCTMCP4921T-E/SNRCT-ND |

| AD9786BSVZRL | 功能描述:IC DAC 16BIT INTERPOL/SP 80TQFP RoHS:是 類別:集成電路 (IC) >> 數據采集 - 數模轉換器 系列:TxDAC+® 產品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:1,000 系列:- 設置時間:1µs 位數:8 數據接口:串行 轉換器數目:8 電壓電源:雙 ± 功率耗散(最大):941mW 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:24-SOIC(0.295",7.50mm 寬) 供應商設備封裝:24-SOIC W 包裝:帶卷 (TR) 輸出數目和類型:8 電壓,單極 采樣率(每秒):* |

| AD9786-EB | 制造商:Rochester Electronics LLC 功能描述:EVAL BOARD FOR AD9786 - Bulk |

| AD9786-EBZ | 功能描述:BOARD EVALUATION FOR AD9786 RoHS:是 類別:編程器,開發系統 >> 評估板 - 數模轉換器 (DAC) 系列:TxDAC+® 產品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:1 系列:- DAC 的數量:4 位數:12 采樣率(每秒):- 數據接口:串行,SPI? 設置時間:3µs DAC 型:電流/電壓 工作溫度:-40°C ~ 85°C 已供物品:板 已用 IC / 零件:MAX5581 |

| AD9786XSV | 制造商:Analog Devices 功能描述:- Bulk |

發布緊急采購,3分鐘左右您將得到回復。