- 您現在的位置:買賣IC網 > PDF目錄300048 > TZ310N TRANSIL PDF資料下載

參數資料

| 型號: | TZ310N |

| 英文描述: | TRANSIL |

| 中文描述: | SCR /二極管模塊 |

| 文件頁數: | 11/11頁 |

| 文件大小: | 389K |

| 代理商: | TZ310N |

9

ATtiny4/5/9/10 [DATASHEET]

8127F–AVR–02/2013

In different addressing modes these address registers function as automatic increment and automatic decrement

(see document “AVR Instruction Set” and section “Instruction Set Summary” on page 150 for details).

4.5

Stack Pointer

The Stack is mainly used for storing temporary data, for storing local variables and for storing return addresses

after interrupts and subroutine calls. The Stack Pointer Register always points to the top of the Stack. Note that the

Stack is implemented as growing from higher memory locations to lower memory locations. This implies that a

Stack PUSH command decreases the Stack Pointer.

The Stack Pointer points to the data SRAM Stack area where the Subroutine and Interrupt Stacks are located. This

Stack space in the data SRAM must be defined by the program before any subroutine calls are executed or inter-

rupts are enabled. The Stack Pointer must be set to point above 0x40. The Stack Pointer is decremented by one

when data is pushed onto the Stack with the PUSH instruction, and it is decremented by two when the return

address is pushed onto the Stack with subroutine call or interrupt. The Stack Pointer is incremented by one when

data is popped from the Stack with the POP instruction, and it is incremented by two when data is popped from the

Stack with return from subroutine RET or return from interrupt RETI.

The AVR Stack Pointer is implemented as two 8-bit registers in the I/O space. The number of bits actually used is

implementation dependent. Note that the data space in some implementations of the AVR architecture is so small

that only SPL is needed. In this case, the SPH Register will not be present.

4.6

Instruction Execution Timing

This section describes the general access timing concepts for instruction execution. The AVR CPU is driven by the

CPU clock clk

CPU, directly generated from the selected clock source for the chip. No internal clock division is used.

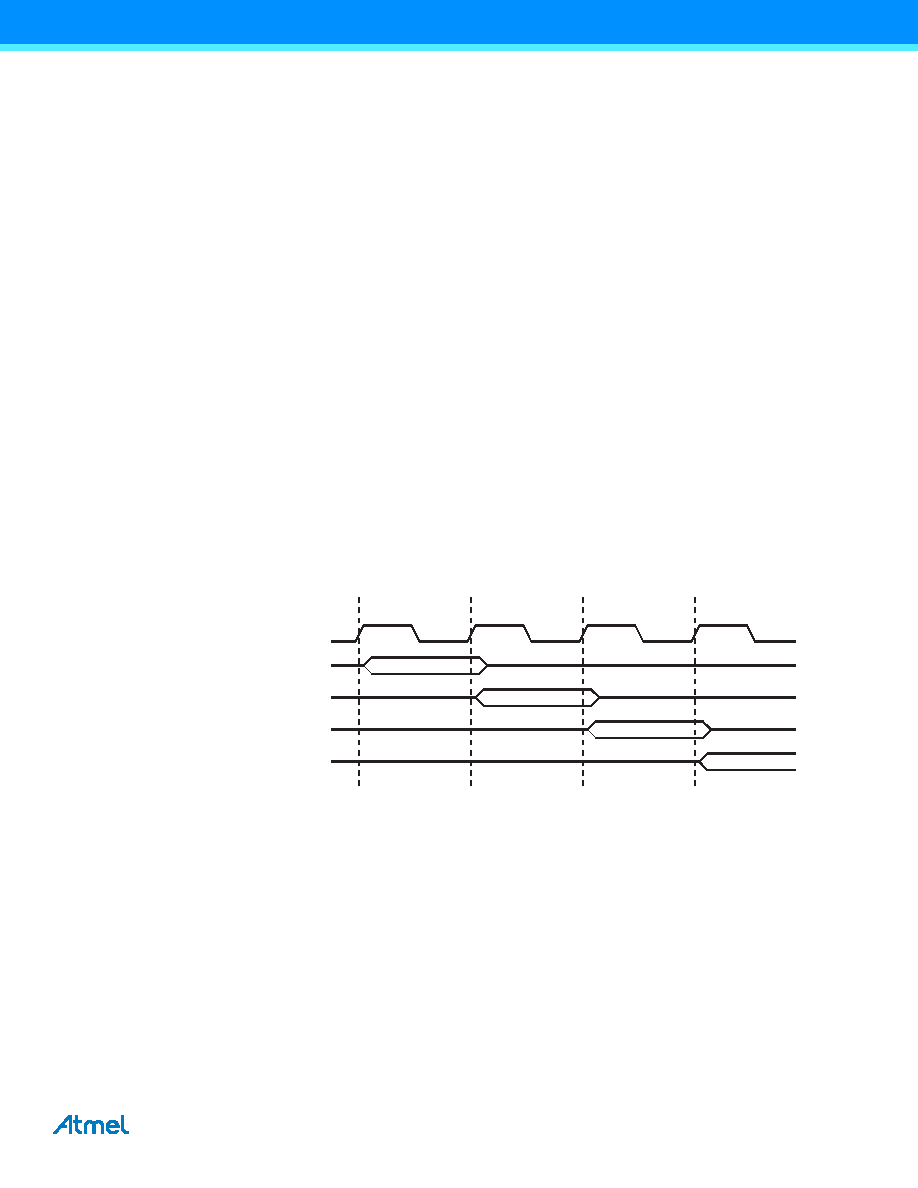

Figure 4-4.

The Parallel Instruction Fetches and Instruction Executions

Figure 4-4 shows the parallel instruction fetches and instruction executions enabled by the Harvard architecture

and the fast access Register File concept. This is the basic pipelining concept to obtain up to 1 MIPS per MHz with

the corresponding unique results for functions per cost, functions per clocks, and functions per power-unit.

Figure 4-5 shows the internal timing concept for the Register File. In a single clock cycle an ALU operation using

two register operands is executed, and the result is stored back to the destination register.

clk

1st Instruction Fetch

1st Instruction Execute

2nd Instruction Fetch

2nd Instruction Execute

3rd Instruction Fetch

3rd Instruction Execute

4th Instruction Fetch

T1

T2

T3

T4

CPU

相關PDF資料 |

PDF描述 |

|---|---|

| TZ335F | TRANSIL |

| TZ530N36KOF | 1500 A, 3600 V, SCR |

| TZ630N28KOF | 1500 A, 2800 V, SCR |

| TZ740N22KOF | 1500 A, 2200 V, SCR |

| TZB6559D51 | INTERCONNECTION DEVICE |

相關代理商/技術參數 |

參數描述 |

|---|---|

| TZ310N20KOF | 功能描述:分立半導體模塊 2000V 700A SINGLE RoHS:否 制造商:Infineon Technologies 產品:Thyristor Power Modules 類型:Phase Controls 安裝風格:Screw 封裝 / 箱體:DT61 封裝: |

| TZ310N22KOF | 功能描述:分立半導體模塊 2200V 700A SINGLE RoHS:否 制造商:Infineon Technologies 產品:Thyristor Power Modules 類型:Phase Controls 安裝風格:Screw 封裝 / 箱體:DT61 封裝: |

| TZ310N24KOF | 功能描述:分立半導體模塊 2400V 700A SINGLE RoHS:否 制造商:Infineon Technologies 產品:Thyristor Power Modules 類型:Phase Controls 安裝風格:Screw 封裝 / 箱體:DT61 封裝: |

| TZ310N25KOF | 制造商:n/a 功能描述:Power Module |

| TZ310N26KOF | 功能描述:分立半導體模塊 2600V 700A SINGLE RoHS:否 制造商:Infineon Technologies 產品:Thyristor Power Modules 類型:Phase Controls 安裝風格:Screw 封裝 / 箱體:DT61 封裝: |

發布緊急采購,3分鐘左右您將得到回復。