- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄293778 > 28230-13 (CONEXANT SYSTEMS) ATM SEGMENTATION AND REASSEMBLY DEVICE, PQFP208 PDF資料下載

參數(shù)資料

| 型號: | 28230-13 |

| 廠商: | CONEXANT SYSTEMS |

| 元件分類: | 數(shù)字傳輸電路 |

| 英文描述: | ATM SEGMENTATION AND REASSEMBLY DEVICE, PQFP208 |

| 封裝: | PLASTIC, MQFP-208 |

| 文件頁數(shù): | 181/237頁 |

| 文件大小: | 3214K |

| 代理商: | 28230-13 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁當(dāng)前第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁第203頁第204頁第205頁第206頁第207頁第208頁第209頁第210頁第211頁第212頁第213頁第214頁第215頁第216頁第217頁第218頁第219頁第220頁第221頁第222頁第223頁第224頁第225頁第226頁第227頁第228頁第229頁第230頁第231頁第232頁第233頁第234頁第235頁第236頁第237頁

35

3.0 Functional Description

3.3 Local Processor Interface

Bt8230

ATM Segmentation and Reassembly Controller—SAR

N8230DS1F

consumers and grants the memory bus to the local processor at the appropriate

time. The local processor is held off during this process by the insertion of a vari-

able number of wait states, accomplished by the i960 withholding READY* or

RDYRCV*. Once the local processor is granted the memory system, the trans-

ceivers are enabled to allow the local processor’s address and data to access the

SRAM or control registers. The conclusion of the data transaction is signaled by

the assertion of PRDY*. Wait states may be inserted by the processor at any time

by asserting PWAIT*. The last data cycle in a burst is indicated by the PBLAST*

signal. In this manner, non-i960 processor half-speed buses or slow transceivers

can be accounted for.

LP_BWAIT [bit 11] in the CONFIG0 register automatically adds a single wait

state between the first access in a burst and subsequent accesses. This can be used

to simplify the design of memory controllers for processors that do not produce a

wait output and which require more time between data cycles in a burst.

3.3.1 Interface Pin Description

The local processor bus interface consists of the control, address, and status sig-

nals described in Table 3-2. As a reference, see Table 1-1, “Hardware Signal Def-

initions,” on page 20.

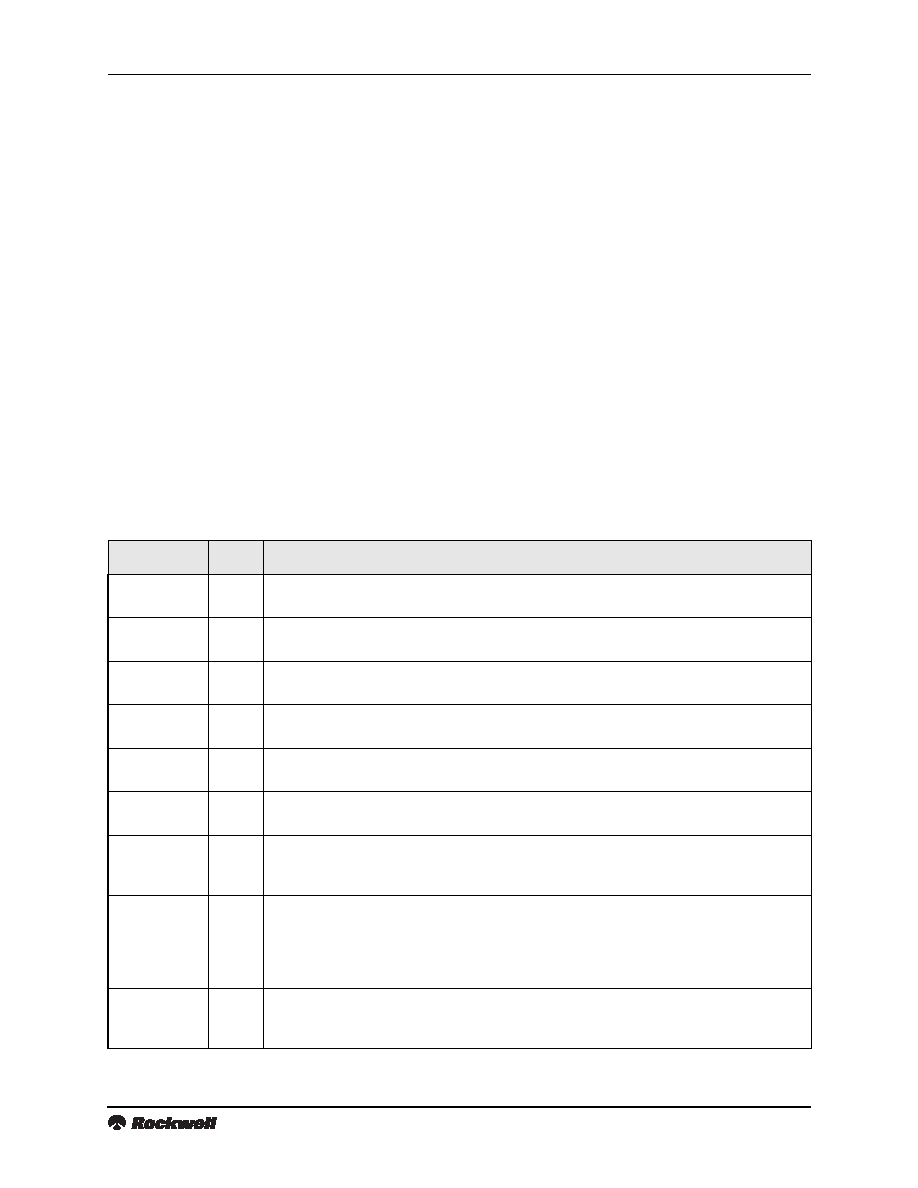

Table 3-2. Processor Interface Pins (1 of 2)

Signal

Dir1

Description

PROCMODE

I

Processor interface mode select input—A logic low on this input enables the local processor mode

of operation.

PCS*

I

Processor interface chip select—A logic low on this signal in conjunction with a logic low on PAS*

at the rising edge of SYSCLK initiates a memory request to the memory controller.

PAS*

I

Processor address strobe— A logic low on this signal in conjunction with a logic low on PCS*

latches the value of PWNR, PBSEL[1,0], PADDR[1,0], and PBE[3:0]* at the rising edge of SYSCLK.

PWNR

I

Processor write/read select—A logic one on this input indicates a write cycle, a logic zero indicates

a read cycle. Latched at rising edge of SYSCLK when PAS* and PCS* are active.

PADDR[1,0]

I

Word select address inputs—Indicates the word address for a single cycle access, or the first word

for a multi-cycle burst access. Latched at rising edge of SYSCLK when PAS* and PCS* are active.

PBSEL[1,0]

I

Bank select inputs—Decode to select MCS[3:0]*; see Figure 3-6 and Table 3-1 for details. Latched

at rising edge of SYSCLK when PAS* and PCS* are active.

PBE[3:0]*

I

Byte select inputs—Active low. Allows individual bytes of selected word to be written. Not active on

reads. Latched at rising edge of SYSCLK when PAS* and PCS* active. PBE[3]* controls writes to

LDATA[31:24], PBE[2]* controls writes to LDATA[23:16], etc.

PWAIT*

I

Processor wait input—Allows processor to insert variable number of wait states to extend memory

transaction. Must be active on rising edge of SYSCLK with PRDY* active to insert wait cycle. May

be used to interface to half speed or slow processor bus or to allow the use of slow transceivers. If

the insertion of wait states is not required, set this input to a logic high. This signal may only be

active (logic low) when PBLAST* is a logic high.

PBLAST*

I

Processor burst last input—Indicates the last word of a cycle. Must be active on rising edge of

SYSCLK with PRDY* active to indicate last cycle. If burst accesses and wait cycles generated by

PWAIT* are not required, this signal should be set to a logic low.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 28L0138-40R | 1 FUNCTIONS, FERRITE BEAD |

| 28L0138-70R | 1 FUNCTIONS, FERRITE BEAD |

| 28Z551 | TELECOM FILTER |

| 28Z550 | TELECOM FILTER |

| 29103BRA | 16K X 1 STANDARD SRAM, 85 ns, CDIP20 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 28230-18-01 | 功能描述:CORD 18AWG NEMA5-15P TO CABLE 制造商:orion fans 系列:- 零件狀態(tài):在售 樣式:公頭插針(刀片)到引線 第一連接器:NEMA 5-15P 第二連接器:線纜 導(dǎo)體數(shù):3 電線類型:SVT 線規(guī):18 AWG 屏蔽:無屏蔽 長度:1.67'(508.0mm) 認(rèn)證標(biāo)記:已注冊 ASTA、BSI Kitemark、CEBEC、CSA、DEMKO、ESTI、FIMKO、IMQ、KEMA、NF、NEMKO、OVE、SEMKO、SAA、T、UL、VDE 認(rèn)證國家/地區(qū):澳大利亞,加拿大,歐洲,芬蘭,日本,荷蘭,新西蘭,挪威,瑞典,英國,美國 顏色:黑色 額定電壓:125VAC 額定電流:10A 工作溫度:60°C 特性:- 標(biāo)準(zhǔn)包裝:1 |

| 282-302 | 制造商:WAGO Innovative Connections 功能描述:END PLATE, RAIL MOUNTED TERMINAL BLOCK; Series:-; Accessory Type:End Plate; For Use With:Rail Mounted Terminal Blocks ;RoHS Compliant: Yes |

| 282302-000 | 功能描述:CABLE 1 COND 12AWG SHIELDED RoHS:是 類別:線纜,導(dǎo)線 >> 單芯導(dǎo)線 系列:- 產(chǎn)品培訓(xùn)模塊:Basics of Wire and Cable 產(chǎn)品目錄繪圖:Stranded Hook Up Wire 標(biāo)準(zhǔn)包裝:1 系列:3070 纜線類型:電子線 線規(guī):24 AWG 線束:7/32 長度:100' (30.5m) 套管類型:聚氯乙烯(PVC) 套管直徑:0.088"(2.24mm) 套管(絕緣體)厚度:0.032"(0.81mm) 電壓:600V 工作溫度:-20°C ~ 105°C 顏色:藍 特點:UL 1015 型 線芯:1 其它名稱:3070 BK005 BLUEA3070L-100 |

| 282304-2 | 制造商:TE Connectivity 功能描述:AMP MODU II RCPT HSG - Bag |

| 28230-439-C | 制造商:Schroff/Pentair Electronic Packaging 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。